# **High Efficiency Integrated Power Solution** for Multicell Lithium Ion Applications

**ADP5080 Data Sheet**

#### **FEATURES**

Wide input voltage range: 4.0 V to 15 V **High efficiency architecture**

Up to 2 MHz switching frequency

6 synchronous rectification dc-to-dc converters

Channel 1 buck regulator: 3 A maximum Channel 2 buck regulator: 1.15 A maximum Channel 3 buck regulator: 1.5 A maximum Channel 4 buck regulator: 0.8 A maximum Channel 5 buck regulator: 2 A maximum

Channel 6 configurable buck or buck boost regulator

2 A maximum for buck regulator configuration

1.5 A maximum for buck boost regulator configuration

Channel 7 high voltage, high performance LDO regulator:

30 mA maximum

2 low quiescent current keep-alive LDO regulators

LDO1 regulator: 400 mA maximum LDO2 regulator: 300 mA maximum

**Control circuit**

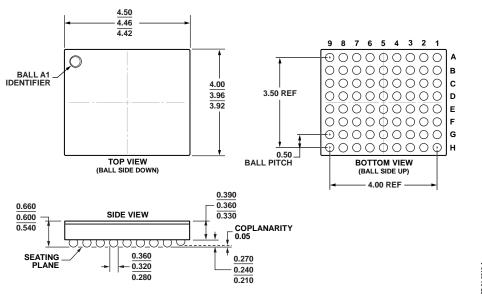

Charge pump for internal switching driver power supply I<sup>2</sup>C-programmable output levels and power sequencing Package: 72-ball, 4.5 mm × 4.0 mm × 0.6 mm WLCSP

(0.5 mm pitch)

# **APPLICATIONS**

**DSLR** cameras Non-reflex (mirrorless) cameras Portable instrumentation

# **GENERAL DESCRIPTION**

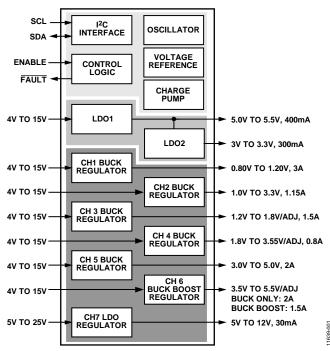

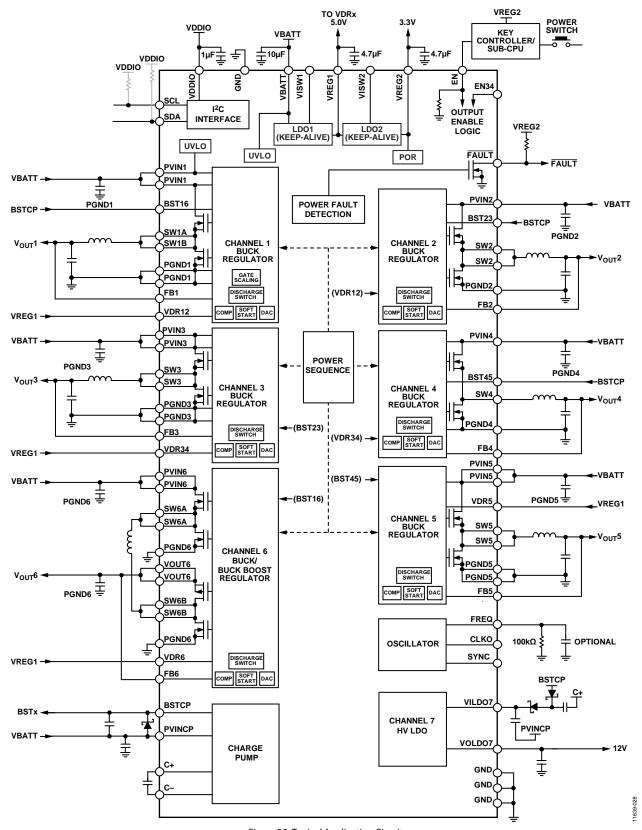

The ADP5080 is a fully integrated, high efficiency power solution for multicell lithium ion battery applications. The device can connect directly to the battery, which eliminates the need for preregulators and, therefore, increases the battery life of the system.

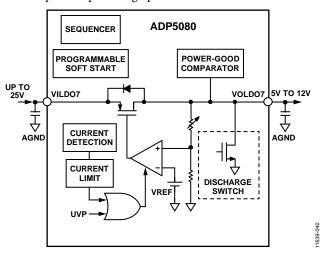

The ADP5080 integrates two keep-alive LDO regulators, five synchronous buck regulators, a configurable four-switch buck boost regulator, and a high voltage LDO regulator. The ADP5080 is a highly integrated power solution that incorporates all power MOSFETs, feedback loop compensation, voltage setting resistor dividers, and discharge switches, as well as a charge pump to generate a global bootstrap voltage.

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

All these features help to minimize the number of external components and PCB space required, providing significant advantages for portable applications. The switching frequency is selectable on each channel from 750 kHz to 2 MHz.

Key functions for power applications, such as soft start, selectable preset output voltage, and flexible power-up and power-down sequences, are provided on chip and are programmable via the I<sup>2</sup>C interface with fused factory defaults. The ADP5080 is available in a 72-ball WLCSP 0.5 mm pitch package.

**Document Feedback**

# **TABLE OF CONTENTS**

| Features                                                                    | 1  |

|-----------------------------------------------------------------------------|----|

| Applications                                                                | 1  |

| Functional Block Diagram                                                    | 1  |

| General Description                                                         | 1  |

| Revision History                                                            | 2  |

| Specifications                                                              | 3  |

| Housekeeping Block Specifications                                           | 4  |

| DC-to-DC Converter Block Specifications                                     | 5  |

| Linear Regulator Block Specifications                                       | 7  |

| I <sup>2</sup> C Interface Timing Specifications                            | 8  |

| Absolute Maximum Ratings                                                    | 9  |

| Thermal Resistance                                                          | 9  |

| ESD Caution                                                                 | 9  |

| Pin Configuration and Function Descriptions                                 | 10 |

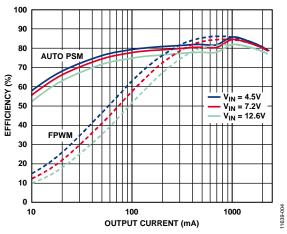

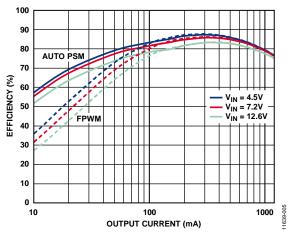

| Typical Performance Characteristics                                         | 12 |

| Application Circuit                                                         | 18 |

| Theory of Operation                                                         | 19 |

| UVLO and POR                                                                | 19 |

| Discharge Switch                                                            | 19 |

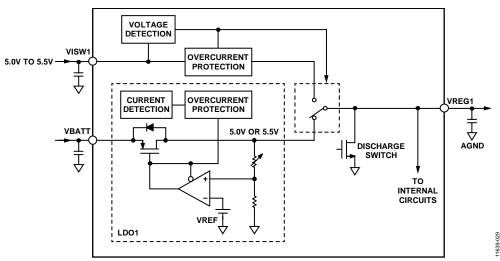

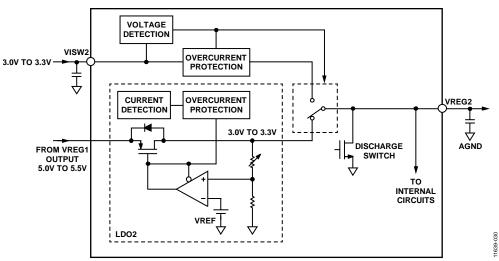

| Keep-Alive LDO Regulators                                                   | 19 |

| DC-to-DC Converter Channels                                                 | 22 |

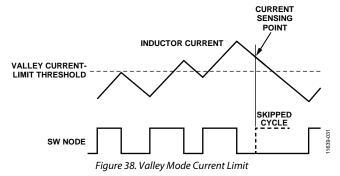

| Light Load and Other Modes of Operation for the DC-to-DC Converter Channels | 27 |

| Switching Clock                                                             |    |

| Soft Start Function                                                         |    |

|                                                                             |    |

| Channel 7: High Voltage LDO Regulator                      | 29 |

|------------------------------------------------------------|----|

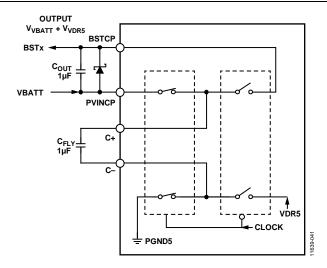

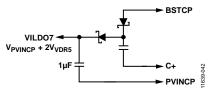

| Charge Pump                                                | 29 |

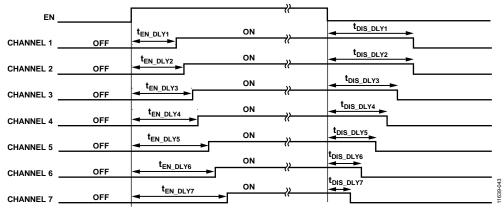

| Enabling and Disabling the Output Channels                 | 30 |

| Power-Good Function                                        | 31 |

| Fault Function                                             | 31 |

| Undervoltage Protection (UVP)                              | 32 |

| Overvoltage Protection (OVP)                               | 33 |

| Applications Information                                   | 34 |

| Component Selection for the Buck and Buck Boost Regulators | 34 |

| Component Selection for the LDO Regulators                 | 36 |

| PCB Layout Recommendations                                 | 36 |

| Thermal Considerations                                     | 37 |

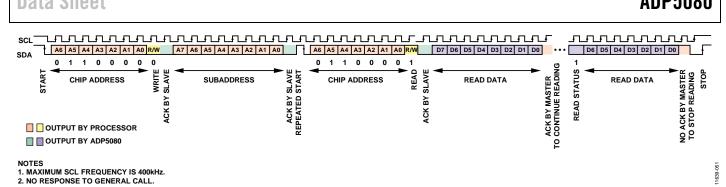

| I <sup>2</sup> C Interface                                 | 38 |

| SDA and SCL Pins                                           | 38 |

| I <sup>2</sup> C Address                                   | 38 |

| Self-Clearing Register Bits                                | 38 |

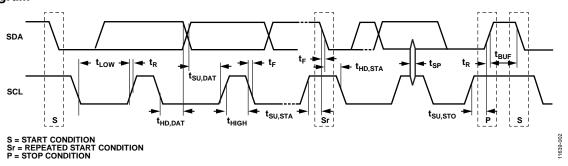

| I <sup>2</sup> C Interface Timing Diagrams                 | 38 |

| Control Register Information                               | 40 |

| Control Register Map                                       | 40 |

| Control Register Details                                   | 41 |

| Factory Default Options                                    | 61 |

| Outline Dimensions                                         | 63 |

| Ordering Guide                                             | 63 |

# **REVISION HISTORY**

4/14—Revision A: Initial Version

# **SPECIFICATIONS**

$T_{J} = 25^{\circ}\text{C}, \ V_{VBATT} = 7.2 \ \text{V}, \ V_{VREG1} = V_{VDRx} = 5 \ \text{V}, \ V_{VREG2} = V_{VDDIO} = 3.3 \ \text{V}, \ unless \ otherwise \ noted.$

Table 1.

| VILDO7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Parameter                   | Symbol                        | Min                      | Тур  | Max                           | Unit | Test Conditions/Comments                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|--------------------------|------|-------------------------------|------|-------------------------------------------------------------------------------------------|

| VILDO7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INPUT SUPPLY VOLTAGE RANGE  |                               |                          |      |                               |      |                                                                                           |

| VDDIO         Vvciolo         1.6         3.6         V           QUESCENT CURRENT<br>Operating Quiescent Current<br>VDDIO         Io york<br>Io york 1 (1000)         8         11         mA         All channels on, nonswitching<br>µA         VVDIO = Vsc1 = Vsca = 3.3 V           Standby Current         Io york 1 (1000)         12         20         µA         All channels on, nonswitching<br>µA         Vyroc = Vsc1 = Vsca = 3.3 V           UNDERVOLTAGE LOCKOUT<br>UVLO Rising Threshold<br>VVLO Falling Threshold<br>VVLO Falling Threshold<br>VVRO (PP)         1.25         mA         All channels on, nonswitching<br>µA         All channels of, nonswitching<br>public Psca = 3.3 V           UVLO Rising Threshold<br>VVRO (PP)         3.45         3.7         3.85         V         At PVIN1<br>At PVIN1           UVLO Falling Threshold<br>VVRO (PP)         3.45         3.55         V         At PVIN1<br>At PVIN1           VESTATE Threshold<br>VVRO (PP)         VVRO (PP)         3.45         3.55         V         At PVIN1<br>At PVIN1           SYNC PIN, Input Clock<br>Frequency Range<br>Minimum Off Pulse Width<br>Minimum Off Pulse Width<br>VVISWO         1.00         ns         Ns         Rosc = 100 kΩ, SEL_FSW = 0           EN Pin<br>High Level Threshold<br>Low Level Threshold<br>VERION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VBATT                       | V <sub>VBATT</sub>            | 4.0                      |      | 15                            | V    | Applies to PVIN1, PVIN2, PVIN3, PVIN4, PVIN5, and PVIN6                                   |

| QUIESCENT CURRENT   Operating Operating Quiescent Current   Operating Quiescent Current   Operating Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VILDO7                      | V <sub>VILDO7</sub>           | 5                        |      | 25                            | V    |                                                                                           |

| Operating Quiescent Current   Operating Quiescent   Operating Quies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VDDIO                       | V <sub>VDDIO</sub>            | 1.6                      |      | 3.6                           | V    |                                                                                           |

| VDDIO   VD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | QUIESCENT CURRENT           |                               |                          |      |                               |      |                                                                                           |

| VDDIO   VD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating Quiescent Current | I <sub>O (VIN)</sub>          |                          | 8    | 11                            | mA   | All channels on, nonswitching                                                             |

| Standby Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                           | IQ (VDDIO OP)                 |                          | 0.2  |                               | μΑ   | _                                                                                         |

| Iq <sub>QNBATI_STIMENZ </sub>   1.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Standby Current             |                               |                          | 12   | 20                            | -    | Includes LDO1 and LDO2, EN low                                                            |

| UNDERVOLTAGE LOCKOUT   UVLO   Rising Threshold   Vuncilla   Vuncilla   Sales   Sales   Sales   Vancilla   Vuncilla   Vuncilla   Sales   Vancilla   Sales   Vancilla   Sales   Vancilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                           | I <sub>Q</sub> (VBATT_STNBY2) |                          | 1.25 |                               | -    | All channels off, EN high,                                                                |

| UVLO Rising Threshold UVLO Falling Threshold VUNLO (Filling Threshold VILING (Filling Threshold Threshold VILING (Filling Threshold Threshold VILING (Filling Threshold Threshold VILING (Filling Threshold Threshold VILING Threshold VILING (Filling Threshold Threshold VIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |                               |                          |      |                               |      | $SEL_FSW = 1$ , $FREQ_CP = 01$                                                            |

| UVLO Falling Threshold         V <sub>VNLO (P)</sub> 3.45         3.55         V         At PVIN1           Reset Threshold         V <sub>VNLO (POR)</sub> 2.4         V         At VBATT, falling           Reset Threshold         V <sub>VNLO (POR)</sub> 2.4         V         At VBATT, falling           SSYNC Pin, Input Clock         fsw         1.98         2.0         2.02         MHz         Rosc = 100 kΩ, SEL_FSW = 0           SYNC Pin, Input Clock         fsrvc         0.5         2.0         MHz         Rosc = 100 kΩ, SEL_FSW = 1           SYNC Pin, Input Clock         fsrvc         0.5         2.0         MHz         Rosc = 100 kΩ, SEL_FSW = 1           SYNC Pin, Input Clock         fsrvc         0.5         2.0         MHz         Rosc = 100 kΩ           Frequency Range         fisrvc         0.5         2.0         MHz         Rosc = 100 kΩ           Minimum On Pulse Width         tsrvc_man_on         100         ns         ns           Might Logic         Vision         0.8 × Vvresc         V         Vvresc₂ = 3.3 V, -25°C ≤ T, ≤ +85           Low Loudi         Vision         0.3 × Vvresc₂         V         Vvresc₂ = 3.3 V, -25°C ≤ T, ≤ +85           Low Level Threshold         Vision         1.45         V         Vv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UNDERVOLTAGE LOCKOUT        | UVLO                          |                          |      |                               |      |                                                                                           |

| VBATT UVLO Threshold<br>Reset Threshold         V <sub>UVLO (BATT)</sub><br>V <sub>UVLO (POR)</sub> 3.3<br>2.4         V         At VBATT, falling<br>At VREG2, falling           OSCILLATOR CIRCUIT<br>Switching Frequency         f <sub>SW</sub> 1.98         2.0         2.02         MHz         Rosc = 100 kΩ, SEL_FSW = 0           SYNC Pin, Input Clock<br>Frequency Range<br>Minimum On Pulse Width<br>Minimum Off Pulse Width<br>High Logic         f <sub>SYNC_MIN_ORF</sub> 0.5         2.0         MHz         Rosc = 100 kΩ           Minimum Off Pulse Width<br>High Logic         t <sub>SYNC_MIN_ORF</sub> 100         ns         Ns           Low Logic         V <sub>L</sub> (SYNC)         0.3 × V <sub>VREG2</sub> V         V <sub>VREG2</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           LOGIC INPUTS<br>EN Pin<br>High Level Threshold         V <sub>L</sub> (EN)         1.45         V         V <sub>VREG2</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           EN34 Pin<br>High Level Threshold         V <sub>L</sub> (EN)         1.45         V         V <sub>VREG2</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           SCL and SDA Pins<br>High Level Threshold         V <sub>L</sub> (EN34)         0.70         V         V <sub>VREG2</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           Low Level Threshold         V <sub>L</sub> (EN34)         0.75 × V <sub>VODIO</sub> V         V <sub>VREG2</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           Low Level Threshold         V <sub>L</sub> (EN34)         0.75 × V <sub>VODIO</sub> V         V <sub>VODIO</sub> = 3.3 V, -25°C ≤ T <sub>J</sub> ≤ +85           Low Level Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UVLO Rising Threshold       | V <sub>UVLO (R)</sub>         | 3.45                     | 3.7  | 3.85                          | V    | At PVIN1                                                                                  |

| Reset Threshold         Vunc (POR)         2.4         V         At VREG2, falling           OSCILLATOR CIRCUIT         Switching Frequency         f <sub>SW</sub> 1.98         2.0         2.02         MHz         Rosc = 100 kΩ, SEL_FSW = 0           SYNC Pin, Input Clock         1.48         1.5         1.52         MHz         Rosc = 100 kΩ, SEL_FSW = 0           Frequency Range Minimum On Pulse Width Minimum Off Pulse Width High Logic         0.5         2.0         MHz         Rosc = 100 kΩ           Low Logic         V <sub>1</sub> (SYNC, MIN, ON)         100         ns         ns         ns           Low Logic         V <sub>1</sub> (SYNC)         0.3 × V/NEG2         V         V/NEG2 = 3.3 V, -25°C ≤ T <sub>1</sub> ≤ +85           LOGIC INPUTS EN High Level Threshold         V <sub>1</sub> (EN)         2.15         V         V/NEG2 = 3.3 V, -25°C ≤ T <sub>1</sub> ≤ +85           EN34 Pin High Level Threshold         V <sub>1</sub> (EN)         1.45         V         V/NEG2 = 3.3 V, -25°C ≤ T <sub>1</sub> ≤ +85           SCL and SDA Pins High Level Threshold         V <sub>1</sub> (EN)         0.70         V         V/NEG2 = 3.3 V, -25°C ≤ T <sub>1</sub> ≤ +85           Low Level Threshold         V <sub>1</sub> (EN)         0.3 × V/NEG2         0.75 × V/NEG0         V         V/NEG2 = 3.3 V, -25°C ≤ T <sub>1</sub> ≤ +85           LOGIC OUTPUTS         SDA Pin         0.4         V         3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UVLO Falling Threshold      | V <sub>UVLO (F)</sub>         |                          | 3.45 | 3.55                          | V    | At PVIN1                                                                                  |

| OSCILLATOR CIRCUIT         Switching Frequency         f <sub>SW</sub> 1.98         2.0         2.02         MHz         Rosc = 100 kΩ, SEL_FSW = 0           SYNC Pin, Input Clock         Frequency Range         f <sub>SYNC</sub> 0.5         2.0         MHz         Rosc = 100 kΩ, SEL_FSW = 1           Frequency Range         Minimum On Pulse Width         100         ns         ns         ns           Minimum Off Pulse Width         100         ns         ns         ns         ns           High Logic         VH (SYNC)         0.3 × V/REG2         V         V/REG2 = 3.3 V, -25°C ≤ T₁ ≤ +85           LOGIC INPUTS         EN Pin         2.15         V         V/REG2 = 3.3 V, -25°C ≤ T₁ ≤ +85           ENA4 Pin         VIL (EN)         1.45         V         V/REG2 = 3.3 V, -25°C ≤ T₁ ≤ +85           Low Level Threshold         VIL (EN34)         1.45         V         V/REG2 = 3.3 V, -25°C ≤ T₁ ≤ +85           SCL and SDA Pins         High Level Threshold         VIL (EN34)         0.70         V/REG2 = 3.3 V, -25°C ≤ T₁ ≤ +85           LOGIC OUTPUTS         SDA Pin         0.3 × V/VDDIO         0.75 × V/VDDIO         V         V/VDDIO = 3.3 V, -25°C ≤ T₁ ≤ +85           Leakage Current         ILEAK (SDA)         10         0.4         V         3.0 mA sink current, -25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VBATT UVLO Threshold        | V <sub>UVLO (BATT)</sub>      |                          | 3.3  |                               | V    | At VBATT, falling                                                                         |

| Switching Frequency       fsw       1.98       2.0       2.02       MHz       Rosc = 100 kΩ, SEL_FSW = 0         SYNC Pin, Input Clock       1.48       1.5       1.52       MHz       Rosc = 100 kΩ, SEL_FSW = 1         Frequency Range       fsync       0.5       2.0       MHz       Rosc = 100 kΩ         Minimum On Pulse Width       tsync_MIN_ON       100       ns         Minimum Off Pulse Width       tsync_MIN_OFF       100       ns         Low Logic       VH,(SYNC)       0.3 × Vyrecg       V       Vyrecg2 = 3.3 V, -25°C ≤ T, ≤ +85         Low Logic       VL,(SYNC)       0.3 × Vyrecg2       V       Vyrecg2 = 3.3 V, -25°C ≤ T, ≤ +85         LOGIC INPUTS       EN Pin       2.15       V       Vyrecg2 = 3.3 V, -25°C ≤ T, ≤ +85         Low Level Threshold       VIL(EN)       1.45       V       Vyrecg2 = 3.3 V, -25°C ≤ T, ≤ +85         Low Level Threshold       VIL(EN34)       0.70       V       Vyrecg2 = 3.3 V, -25°C ≤ T, ≤ +85         SCL and SDA Pins       High Level Threshold       VIL(EN34)       0.75 × Vyrodo       V       Vyrodo = 3.3 V, -25°C ≤ T, ≤ +85         Low Level Threshold       VIL(EXC)       0.3 × Vyrodo       V       Vyrodo = 3.3 V, -25°C ≤ T, ≤ +85         Low Level Threshold       VIL(EXC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reset Threshold             | V <sub>UVLO (POR)</sub>       |                          | 2.4  |                               | V    | At VREG2, falling                                                                         |

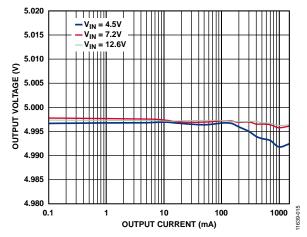

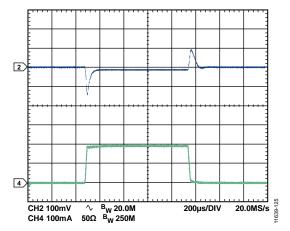

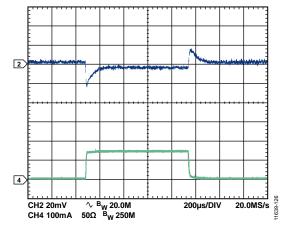

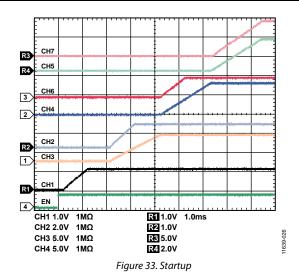

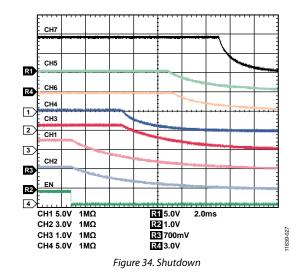

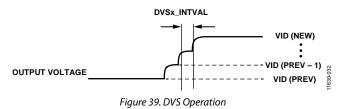

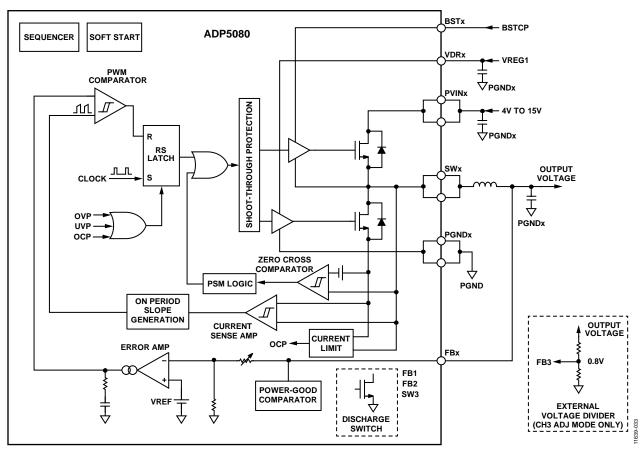

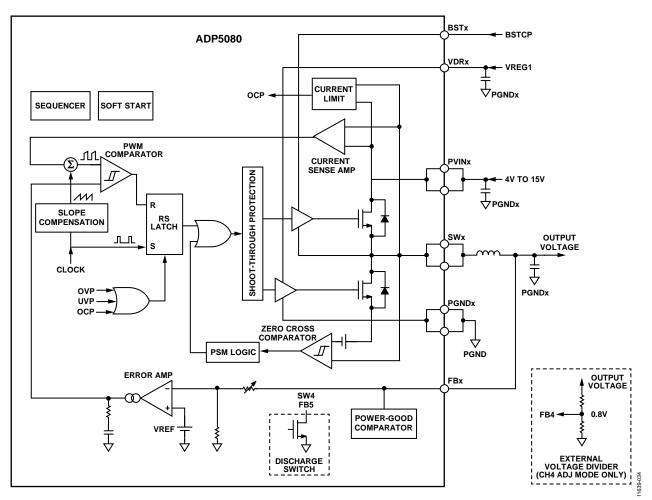

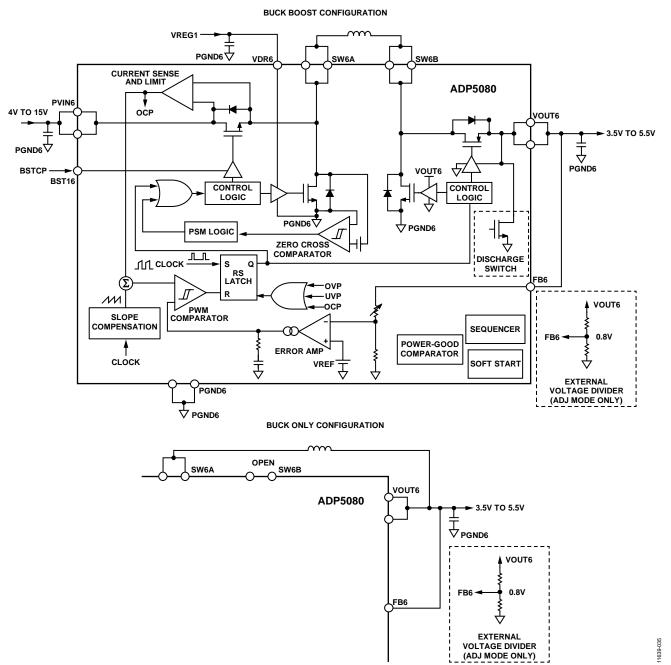

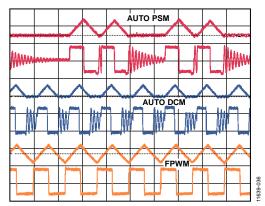

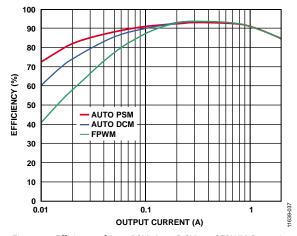

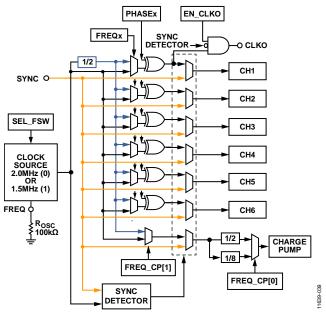

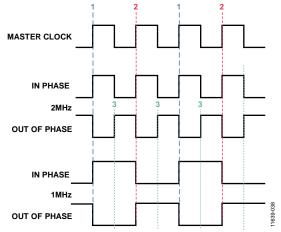

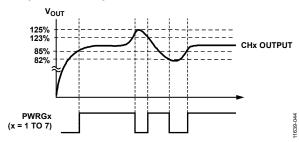

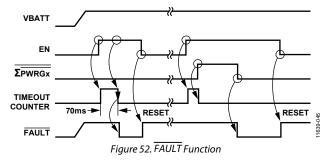

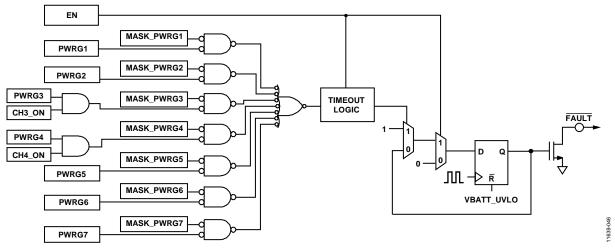

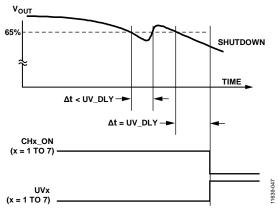

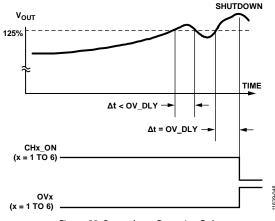

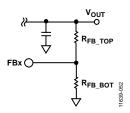

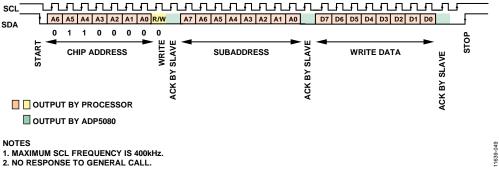

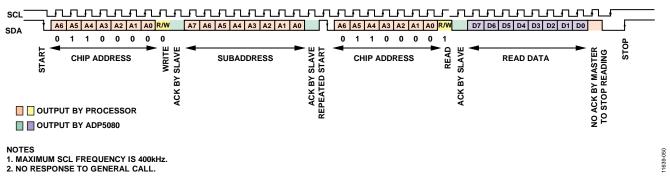

| SYNC Pin, Input Clock Frequency Range Minimum On Pulse Width Minimum Off Pulse Width High Logic Low Logic  V <sub>I</sub> (SYNC)  LOGIC INPUTS EN Pin High Level Threshold Low Level Threshold V <sub>I</sub> (EN) High Level Threshold V <sub>I</sub> (EN)  V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (EN) V <sub>I</sub> (E | OSCILLATOR CIRCUIT          |                               |                          |      |                               |      |                                                                                           |